Testing and Packaging of Silicon Photonic Chips: A Comprehensive Guide

- Latitude Design Systems

- Mar 4, 2024

- 4 min read

Silicon photonics, the integration of optical and electronic functionalities on a silicon chip, has revolutionized various fields including high-speed data communication, optical sensing, and biophotonics. However, ensuring the functionality and performance of these chips requires robust testing and packaging strategies. This article delves into the essential aspects of testing silicon photonic chips, exploring both electrical and optical interfacing techniques, design for testability (DFT) considerations, and the implementation of automated optical probe stations for high-throughput characterization.

Electrical and Optical Interfacing Techniques

Testing silicon photonic devices necessitates efficient interfacing between the electrical and optical domains. Here are two primary methods:

Wire Bonding and On-Chip Probes: Electrical connections are established using wire bonding, where thin wires connect the chip's electrical pads to a test board or package. For high-frequency measurements, on-chip probes with precise positioning capabilities are employed. These probes, such as Ground-Signal-Ground (GSG) probes, ensure proper contact with the chip's electrical pads [1].

Optical Fiber Coupling: Light is coupled into and out of the silicon chip using optical fibers. Grating couplers, fabricated on the chip, facilitate efficient light transfer between the waveguide on the chip and the optical fiber. The spacing between the fiber and the chip is crucial, typically ranging from 5 to 50 micrometers. Polarization-maintaining (PM) fibers are often preferred to minimize signal degradation due to polarization effects in silicon waveguides.

Design for Testability (DFT) Considerations

Integrating DFT principles during the chip design stage streamlines the testing process and facilitates failure analysis. Here are key considerations:

Test Structures: These on-chip structures allow for local metrology and characterization of material properties, waveguide losses, and device functionalities like coupling coefficients and modulation efficiency. Examples include ring resonators, waveguides of varying widths, and directional couplers. These structures can be monitored to assess fabrication process uniformity and device performance.

Trimming: Fabrication non-uniformities and temperature sensitivity of silicon necessitate trimming for phase-sensitive circuits like Mach-Zehnder modulators and ring resonators. Trimming can be achieved on-chip via thermal tuning or carrier injection, or through post-processing techniques like selective annealing.

Optical Power Budget: Understanding the available optical power, transmission losses, and detector sensitivity is paramount. A power budget analysis calculates the total optical loss throughout the system, encompassing fiber coupling losses, waveguide propagation losses, and insertion losses of on-chip devices. This helps determine if sufficient power reaches the detector for accurate signal measurement.

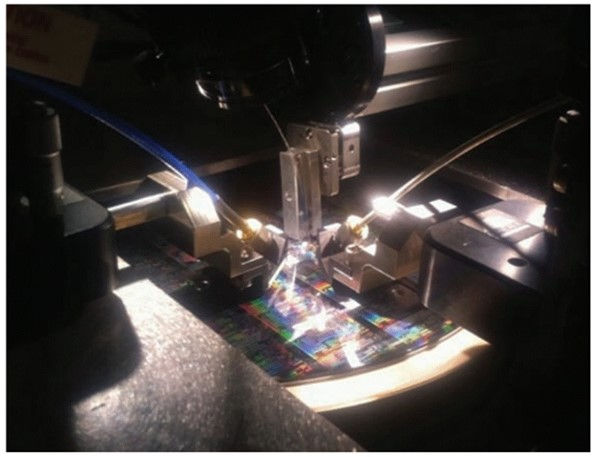

Automated Optical Probe Stations

For high-throughput testing and characterization, automated optical probe stations offer significant advantages. These systems integrate various components to precisely align the silicon photonic chip with an optical fiber array, enabling automated optical measurements. Here's a breakdown of the core components and their functionalities:

Sample Stage: This stage, controlled by stepper motors, precisely positions the silicon photonic chip relative to the optical fiber array. It typically offers travel ranges exceeding 100 mm to accommodate various die sizes. Resolution and repeatability better than 1 µm are crucial for accurate fiber-chip alignment.

Optical Fiber Array: The fiber array comprises multiple optical fibers arranged in a V-groove configuration. This allows for simultaneous alignment of all fibers with the chip's grating couplers, accelerating the testing process. Polarization-maintaining (PM) fibers with FC/APC connectors are commonly used to minimize reflections and address polarization sensitivity in silicon photonics.

Micro-Positioners and Piezo-Nano-Positioners: These high-precision actuators enable precise alignment of the fiber array relative to the chip's grating couplers. Piezoelectric stages offer nanometer-scale positioning capabilities for fine-tuning the alignment. Stepper motor controllers often utilize optical encoders to enhance accuracy.

Custom Chip Mount: This mount securely holds the silicon photonic sample. It may incorporate a vacuum chuck and a thermoelectric module with a thermistor for temperature control, ensuring stable testing conditions.

Microscope and Camera: An optical microscope with a camera facilitates visual inspection and alignment during the testing process. The camera captures images of the fiber array and chip, enabling precise alignment adjustments.

Control Software: Open-source software manages communication between the various components of the probe station. It automates alignment procedures, data acquisition from connected equipment like tunable lasers and detectors, and controls external electrical test equipment.

Operational Procedures:

The software typically follows a standardized approach:

Retrieving Device Locations: The software extracts the coordinates of the grating couplers on the silicon photonic chip from the layout design file.

Automated Alignment: Micro-positioners move the fiber array to precisely align each fiber with its designated grating coupler on the chip. Coarse and fine alignment steps are employed for efficient positioning.

Chip Registration: After successful alignment, the software registers the chip’s physical location relative to the fiber array for subsequent automated testing.

Automated Testing: Based on a pre-defined test list, the software automatically aligns the chip with each device under test. Measurements, such as optical spectrum acquisition using a tunable laser and detector, are performed sequentially. Electrical characterization can also be integrated, with the software controlling electrical probes to contact the chip’s electrical pads and acquire necessary measurements.

Additional Considerations

Optical Test Equipment: The selection of optical test equipment depends on the specific characterization needs. Tunable lasers with low linewidth and high stability are essential for resolving resonator linewidths and measuring devices with high extinction ratios. Optical amplifiers can be used to boost signal strength, but their noise characteristics and potential spectral filtering requirements need consideration. For high-speed measurements, electrical vector network analyzers, signal generators, oscilloscopes, and bit error rate testers are often employed.

Packaging: Once testing is complete, the silicon photonic chip is packaged to provide environmental protection, facilitate fiber coupling, and ensure reliable operation in the intended application. Common packaging approaches include coupling the chip with a fiber array pigtail using passive alignment techniques or active alignment mechanisms for high-precision applications.

Conclusion

Testing and packaging are crucial steps in the development and deployment of silicon photonic chips. A thorough understanding of electrical and optical interfacing techniques, design for testability principles, and the functionalities of automated optical probe stations empowers researchers and engineers to efficiently characterize and validate the performance of these integrated photonic devices. By following the outlined procedures and considerations, users can establish robust testing methodologies for their silicon photonic chip development endeavors.

Reference

[1] L. Chrostowski and M. Hochberg, Silicon Photonics Design: From Devices to Systems. Cambridge, UK: Cambridge University Press, 2015.

[2] Bradley W. Snyder and Peter A. O’Brien. “Developments in packaging and integration for silicon photonics”. Proc. SPIE. Vol. 8614. 2013, pp. 86140D–86140D–9. doi: 10.1117/12.2012735.

[3] PLC Connections PLCC – Silicon Photonics. [Accessed 2014/04/14]. url: http://www. plcconnections.com/silicon.html.

[4] Paul E. Barclay, Kartik Srinivasan, Matthew Borselli, and Oskar Painter. “Probing the dispersive and spatial properties of photonic crystal waveguides via highly efficient coupling from fiber tapers”. Applied Physics Letters 85.1 (2004).

Comments